Диагностика и неисправности мультиконтроллера в ноутбуке

В этой статье пойдет речь о микросхеме, которая управляет работой всего ноутбука, в том числе, его включением. Её неисправности приводят к значительным последствиям для пользователя и чаще всего требуют ремонта материнской платы в сервисе.

Задачи мультиконтроллера

Мультиконтроллером, или, по-английски Super I/O (SIO) или Multi I/O (MIO), на сленге «мультик» (еще в документации встречается EC-контроллер), называется микросхема, обеспечивающая мониторинг напряжений и температур, работу с периферийными устройствами. Такими устройствами могут быть клавиатура, мышь, кнопка включения, датчик закрытия крышки и тп. Основным его предназначением является управление клавиатурой (даже в схемах он обозначается как KBC-контроллер), однако со временем производители начали нагружать его множеством дополнительных функций, таких, например, как индикация работы жесткого диска (светодиод на передней панели ноутбука) или управление частотой работы кулера. Именно на эту микросхему «приходят» все контактные дорожки шлейфа клавиатуры ноутбука. На самом деле на ножки мультиконтроллера приходят сигналы практически со всех устройств и микросхем ноутбука. Уровень сигнала может быть постоянный 3.3V (высокий логический уровень), либо изменяющийся в случае обмена данными (измеряется осциллографом).

В запуске ноутбука он вообще играет первостепенную роль, так как именно на него приходит сигнал с кнопки включения, и именно он запускает все источники напряжений и затем отдает сигнал южному мосту для начала инициализации.

Мультиконтроллер управляет включением ШИМ-контроллеров, вырабатывающих необходимые для работы узлов ноутбука напряжения, ключами, коммутирующими эти напряжения. Через мультиконтроллер по протоколу Firmware HUB или SPI подключена микросхема Flash c программным обеспечением (которую иногда приходятся прошивать). В состав мультиконтроллера могут входить контроллеры часов реального времени, жестких дисков, USB, интегрированный аудиоинтерфейс, интерфейс LPC.

Разновидности мультиконтроллеров

Мультиконтроллеры выпускают следующие фирмы: ENE; Winbond; Nuvoton; SMCS; ITE; Ricoh.

Сильно отличаются только последние, хотя бы методом пайки, они BGA.

На современных мультиконтроллерах имеется по 128 ножек, но их назначение сильно отличатся в зависимости от модели мультиконтроллера и даже от его ревизии. К примеру, KB926QF-D2 и KB926QF-C0. — два совершенно разных мультиконтроллера.

Неисправности мультиконтроллеров и их симптомы

Мультиконтроллер часто выходит из строя при залитии ноутбука жидкостью или вследствие выгорания ключей, формирующих 3.3В. Второе случается при скачках питания в сети.

К основным симптомам неисправности мультиконтроллера можно отнести некорректную работу клавиатуры и тачпада и отсутствие запуска как такого. Также, следствием неправильной работы «мультика» являются и глюки периферии — неправильная работа датчиков, кулера. Также по вине SIO может не определяться жесткий диск и другие накопители (работа USB при этом завязана на южный мост).

В диагностике и ремонте ноутбуков мультиконтроллер имеет ключевое значение, поскольку отсутствие на мультиконтроллере важных сигналов, приходящих с микросхем ноутбука, позволяет выявить неисправные микросхемы и произвести их замену. На мультиконтроллер приходит LPC шина, по который идет обмен с южным мостом, и с которой можно считать всем известные POST-коды. Для этого, кстати, в ремонте часто подпаиваются на прямую к ножкам мультиконтроллера тоненькими проводками и выводят коды на индикаторы.

Также иногда во время самостоятельной замены матрицы ноутбука забывают отключить аккумулятор. Это тоже может привести к выгоранию мультиконтроллера. Но, к счастью, микросхемы эти не очень дорогие и ремонт такой неисправности обходится дешевле, чем, например, замена южного моста или видео. Многие микросхемы взаимозаменяемы, а перепайка их — 15 минут (если не потребуется прошивать флэш память).

Диагностика запуска (или отсутствия старта) ноутбука

Для правильной диагностики старта ноутбука необходимо понимать его последовательность и участие в нем мультиконтроллера.

Последовательность включения ноутбука

При включении ноутбука дежурное напряжение через кнопку подается на мультиконтроллер, который запускает все ШИМ-контроллеры, вырабатывающие все напряжения (их много), и, при нормальном исходе, вырабатывают сигнал PowerGood. По этому сигналу снимается сигнал RESET с процессора и он начинает выполнять программный код, записанный в BIOS с адресом FFFF 0000.

Затем BIOS запускает POST (Power-On Self Test), который выполняет обнаружение и самотестирование системы. Во время самотестирования обнаруживается и инициализируется видеочип, включается подсветка, определяется тип процессора. Из данных BIOS определяется его тактовая частота, множитель, настройки. Затем определяется тип памяти, ее объем, проводится ее тестирование. После этого происходит обнаружение, инициализация и проверка подключенных накопителей – привода, жесткого диска, карт-ридера, флоппи дисковода и др., а после проверка и тестирование дополнительных устройств.

После завершения POST управление передается загрузчику операционной системы на жестком диске, который и загружает ее ядро.

Из описания выше видно, что мультиконтроллер вступает в работу на самой ранней стадии, и без его нормального запуска не сформируются управляющие напряжения. Вот условия, необходимые для того, чтобы мультиконтроллер дал команду на старт:

- Основной BIOS и EC-BIOS должны быть рабочие.

- Мультиконтроллер запитан, работает его кварц и мульт вычитывает содержимое BIOS

- ACIN = 3.3 V

- LID_SW# = 3.3V (крышка ноутбука открыта)

- EC_RST# = 3.3V (мульт снимает RESET с южного моста)

- Южный мост снимает сигналы PM_SLP_S3# и SLP_S5#, то есть, на них устанавливается 3.3V

- При нажатии кнопки включения сигнал ON/OFFBTN# падает до нуля и этот же сигнал транслируется в PBTN_OUT#

Для инициализации мультиконтроллера необходима микропрограмма, которая хранится либо в той же микросхеме флеш-памяти, что и прошивка BIOS (UEFI), либо в отдельной микросхеме меньшего объема, либо внутри самого мультиконтроллера. В первых двух случаях восстановить прошивку не представляется сложным. А вот прошить непосредственно мультиконтроллер пока могут не любые программаторы. Да и подключиться к нужным его выводам не всегда просто. Прошиваемые мультиконтроллеры — NPCE288N/388N, KB9010/9012/9016/9022, IT8585/8586/8587/8985/8987.

Лучше всего найти документацию и описание сигналов по мультикам IT, которые используются во многих бюджетных ноутбуках, в том числе ASUS и Dell. Благодаря схемам можно понять и отследить, где находятся выше указанные сигналы. Например, в случае IT8752 и аналогичных (используется, например, в семействе ASUS K40 и K50) для диагностики вас должны интересовать, помимо выше указанных, следующие сигналы на мультике:

- ALL_SYSTEM_PWRGD (68 мульт)

- SUS_PWRGD (67 мульт)

- VRM_PWRGD (1 ISL6262)

Входящие сигналы указывают на выработку сигнала PowerGood и наличие питания Suspend режима и питания на VRM регуляторе ISL6262. Это значит, мост и процессор запитаны. - Сигналы H_CPURST#_XDP и H_PWRGD_XDP разрешают работу процессора.

- PWR_SW# — сигнал с кнопки включения

- CPU_VRON — включения питания на CPU

- PM_RSMRST# — снимает RESET с моста

- PM_SUSB# — хаб PCH должен выдать сигналы PM_SUSC# и PM_SUSB# идущие на мульт, а мульт в ответ выдать сигналы SUSC_EC# и SUSB_EC#

- PM_PWROK — сигнал на хаб, что питание в норме

- PM_CLKRUN# — сигнал на запуск тактирования

- PM_PWRBTN# — сигнал на включение южного моста

- VSUS_ON — сигнал включения дежурного питания на силовых ключах

- EC_CLK_EN (CLK_EN#) — разрешение тактирования на южный мост

Питание на IT85xx мульты поступает следующее: +3VA_EC, +3VPLL, +3VACC, без них микросхема не запустится.

Последовательность диагностики мультиконтроллера

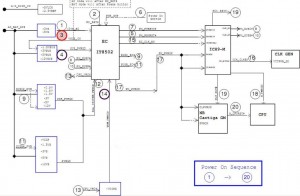

Рассмотрим схему последовательности включения ноутбука:

Для диагностики в целом, вам нужно рассмотреть две ситуации:

1. Питание не появляется, светодиод питания не горит.

2. Питание есть, светодиод питания горит, но ноутбук не включается, экран темный. Индикатор жесткого диска сначала включается и гаснет, затем не горит.

Очевидно, мультик работает, управляющие сигналы формируются, однако, дальнейший запуска не происходит или он обрывается. Чаще всего виноваты в этом микросхемы чипсета, сам процессор или тактирующие генераторы, которые срывают генерацию сигналов. Для быстрой диагностики прогреваем микросхемы чипсета по-очереди. После каждого прогрева пробуем на включение. Если ноутбук включается, то виноват конкретный чип. Очень важна предыстория поломки — например, если до поломки перестали работать USB порты, то скорее всего вышел из строя южный мост. Если были артефакты на встроенном видео, то виноват северный мост.

Если же мы видим, что питающие напряжения присутствие, а сигналы с мультика нет (например, не снимается сигналы RESET), то изучаем все сигналы более подробно.

Вот обобщенный порядок следования сигналов при запуске EC:

2в или ACIN_OC#=0в

вычитка прошивки SPI ROM

-> сигнал включения силовых дежурок VSUS_ON=3в

-> снятие ресета с юга PM_RSMRST#=3в (юг узнает, что первичные источники питания ок)

-> сигнал PM_PWRBTN#=0в транслируется в юг

-> SUSB_EC#, SUSC_EC# = 3в включение вторичных источников и открытие коммут. мосфетов

-> CPU_VRON=3в поднятие питания CPU_VCORE процессора

-> EC_CLK_EN (CLK_EN#) на юг или на тактовый генератор приходит с мульта или ШИМ проца

-> VRM_PWRGD_CLKEN приходит на юг

-> CLK_PWRGD с юга приходит на тактовый генератор

-> сигнал PWROK на юг

-> юг отдает процу сигнал H_PWRGD (HardWare PWRGD, все питания в порядке, следующий этап инициализации)

-> юг снимает ресет с севера PLT_RST#

-> юг снимает ресет с PCI шины PCI_RST#

-> север снимает ресет с процессора HCPU_RST#

Вот алгоритм проверки популярного мульта KB3926, его можно применить и к аналогам:

- Проверить питание мульта 3,3v (9 нога)

- Проверить генерацию кварца (123 нога)

- Проверить сигнал с кн.вкл. ON/OFF 3,3v/0,5v (32 нога)

- Проверить АCCOF 0V (27 нога)

- Проверить ACIN 3.1V (127 нога)

- Проверить PBTN_OUT 0v/3,3v (117 нога)

- Проверить сигнал 0v/3,3v (14 нога)

- Проверить RSMRST 0v/3,3v (100 нога)

- Проверить PWROK 0v/3,3v (104 нога)

- Проверить SYSON 0v/3,3v (95 нога)

- Проверить VRON 0v/3,3v (121 нога)

- Проверить обмен мульта с югом 3,3v (77,78 нога)

- Проверить обмен мульта с югом 0v/3,3v (79,80 нога)

- Проверить генерацию PCICLK (12 нога)

- Проверить сигнал 0v/3,3v (1,2,3 нога)

- Проверить TP_CLK 0v/0,1v (87 нога)

- Проверить TP_DATA 0v/5v (88 нога)

- Проверить SUSP 0v/3,3v (116 нога)

- Проверить VGA_ON 0v/3,3v (108 нога)

Вот дополнительные контрольные значения напряжения:

DPWROK_R — 3,3V

PM_RSMRST#PCH — 3,3V

PM_RSMRST#- 3,3V

SUS_PWRGD — 3,3V

5VSUS_PWRGD — 3,3V

ME_SUSPWRDNACK_R — 3.3V

Как видно из алгоритма, в самом начале EC контроллер должен вычитать прошивку из Flash памяти через SPI интерфейс. Если этого не происходит, то дальше никаких сигналов питания ШИМов не формируется. Часто, в случае серии IT85xx и аналогичных это отдельня 8-контактная микросхема (напримерб SST25VF080B) с питанием по линии +3VA_SPI. Обмен данными происходит по линия SO и SI, тактирование по линии SCK. Поэтому, когда это возможно, флэшку перешивают. В некоторых сервисах имеется специальный программатор от Сергея Вертьянова, который позволяет прошивать почти любые флэшки:

Нажмите на звезду, чтобы оценить мои труды!

Источник

ISA умер! Да здравствует LPC?

Сегодня в персональном компьютере осталось только одно функциональное устройство, по которому можно проследить его генеалогию, — это интерфейс ISA, доставшийся ему по наследству от IBM PC AT. Большинство карт расширения выполняется по стандарту PCI, многие видеокарты подключаются по AGP. Однако производители карт расширения и материнских плат кивают друг на друга: если стандарт существует, то под него должны выпускаться карты; если выпускаются карты с интерфейсом ISA, то материнские платы должны его поддерживать. В спецификации PC98 наличие разъемов расширения стандарта ISA признается нежелательным. Однако для подсоединения таких устройств, как параллельные и последовательные порты, клавиатура, флоппи-диск, какой-нибудь интерфейс все же необходим. Поэтому разработчики микросхем для материнских плат вынуждены разводить ISA на кристалле, а чтобы добро не пропадало зря, — и выводить его наружу. Что же придет ему на смену?

| Наименование | Направление | Назначение | |

|---|---|---|---|

| Периферия | Основной задатчик | ||

| LAD[3:0] | I/O | I/O | Мультиплексированные команды, адреса и данные |

| LFRAME# | I | O | Фрейм, указывает на начало новой команды |

| LRESET# | I | I | Сброс, те же функции, что PCI Reset. При наличии PCIRST# необязателен |

| LCLC | I | I | Тактовая частота 33 МГц, те же функции, что PCICLK |

Для подключения перечисленных выше устройств Intel предлагает новый стандарт — LPC (Low Pin Count, Малое Количество Контактов). Этот интерфейс, по утверждению представителей корпорации, будет встраиваться в будущие чипсеты для материнских плат. Такие намерения Intel означают, что, вероятнее всего, мы вскоре сможем в добровольно-принудительном порядке ознакомиться со стандартом LPC. Попробуем сделать это заранее и по собственной воле.

Введение нового стандарта преследует следующие цели:

- убрать из системы ISA и X-bus;

- снизить стоимость системы;

- обеспечить скорость обмена, не меньшую, чем по шине X-bus;

- предоставить те же типы циклов, что и X-bus;

- увеличить адресуемое пространство с традиционных 16 Мбайт до 4 Гбайт;

- значительно упростить временные диаграммы за счет синхронной природы интерфейса;

- обеспечить прозрачность для программного обеспечения и отсутствие конфликтов из-за ресурсов;

- обеспечить пригодность как для настольных, так и для мобильных систем;

- обеспечить функции управления потребляемой мощностью.

Контактов действительно очень мало: семь обязательных (для передачи информации) и шесть дополнительных (для подключения устройств, выполняющих функцию задатчика и управления мощностью). Названия и функции обязательных сигналов интерфейса LPC приведены в табл. 1. Команды, адреса и данные передаются по линиям LAD[3:0] тетрадами-нибблами последовательно по четыре бита за один раз. Подобно PCI интерфейс синхронный, каждый цикл состоит из нескольких полей, каждое из которых имеет длительность в один период тактовой частоты 33 МГц. Любой цикл обмена по интерфейсу LPC начинается с того, что основной задатчик на шине (обычно чипсет) устанавливает активный уровень на линии LFRAME#. При этом все периферийные устройства переходят в состояние «начало цикла» и анализируют состояние линий LAD[3:0]. Если устройства передавали информацию по линиям LAD[3:0], то они немедленно их освобождают. Таким образом, этот сигнал может использоваться для прекращения затянувшихся циклов, например, при сбоях и зависаниях. То есть при достаточно интеллектуальном основном задатчике зависшее периферийное устройство не сможет подвесить всю систему. Сигнал LFRAME# может быть активным более одного периода тактовой частоты 33 МГц. В этом случае действительной считается информация, имевшаяся на LAD[3:0] во время последнего периода тактовой частоты. Первое поле — START — определяет тип операции, его возможные значения приведены в табл. 2.

| Значение LAD[3:0] | Тип операции |

|---|---|

| 0 | Начало ввода/вывода или чтения/записи |

| 1 | Зарезервировано для последующего расширения |

| 10 | Разрешение для задатчика номер 1 |

| 11 | Разрешение для задатчика номер 2 |

| 0100-1110 | Зарезервировано для последующего расширения |

| 1111 | Принудительное прекращение цикла |

Следующее поле — CYCTYPE + DIR (Cycle Type / Direction, тип цикла и направление передачи), определяется текущим задатчиком. Это поле может иметь значения, указанные в табл. 3. Значение бита LAD[0] зарезервировано, и он всегда должен быть равен 0.

Поле SIZE (Размер) может принимать значения 00 при передаче 1 байта, 01 при передаче 2 байт и 11 при передаче 4 байт. Значение 10 зарезервировано. Это поле используется только при операциях прямого доступа; ввод/вывод и чтение/запись осуществляются побайтно. Поле ADDR имеет длину четыре периода тактовой частоты для операций ввода/вывода и восемь периодов для циклов обращения к памяти. Адреса передаются начиная со старшей тетрады, то есть при обращении к памяти первыми передаются биты 31:28, а последними — 3:0.

| LAD[3:2] | LAD[1] | Тип операции |

|---|---|---|

| 0 | 0 | Чтение из внешнего устройства |

| 0 | 1 | Запись во внешнее устройство |

| 1 | 0 | Чтение из памяти |

| 1 | 1 | Запись в память |

| 10 | 0 | Прямой доступ к памяти для чтения |

| 10 | 1 | Прямой доступ к памяти для записи |

| 11 | Х | Зарезервировано. Периферия должна игнорировать это значение, а основной задатчик, обнаружив его, прерывает цикл установкой LFRAME# в активное состояние |

Поле CHANNEL используется в операциях прямого доступа к памяти и содержит в битах 0:2 номер канала, а в бите 3 — аналог сигнала Terminal Count шины ISA.

Поле DATA (Данные) имеет длину два периода тактовой частоты и содержит данные, передаваемые младшей тетрадой вперед. В одном цикле может содержаться одно, два или четыре поля DATA.

Поле передачи управления Turn Around, TAR, используется для передачи контроля над линиями LAD [3:0] второму участнику данного цикла, что необходимо при операциях чтения. Оно имеет продолжительность два периода тактовой частоты, на первом периоде текущий задатчик устанавливает на линиях LAD[3:0] значение 1111, на втором отключается, ожидая информацию от второго участника диалога.

Поле SYNC служит для синхронизации источника и приемника данных. Его вставляет ведомый участник цикла для того, чтобы подготовить для передачи запрошенные данные, или для размещения полученной информации. Полей SYNC в одном цикле может быть несколько, фактически столько, сколько нужно для подготовки. Значения поля SYNC приведены в табл. 4.

| LAD[3:0] | |

|---|---|

| 0 | Синхронизация достигнута |

| 0001-0100 | Зарезервировано |

| 101 | Короткое ожидание |

| 110 | Длительное ожидание, будет добавлено много полей SYNC |

| 0111-1000 | Зарезервировано |

| 1001 | Синхронизация достигнута, передача будет продолжена в следующем цикле (только при прямом доступе к памяти) |

| 1010 | Ошибка. В переданных данных содержится ошибка |

| 1011 — 1111 | Зарезервировано |

Значение 1010 — Ошибка необходимо потому, что все циклы должны иметь определенную длину, так что периферийное устройство обязано передать требуемое для данного цикла количество данных, но перед этим оно честно предупреждает задатчика о том, что эти данные имеют чисто фиктивный характер.

Ознакомившись с типами полей, можно более подробно рассмотреть механизмы начала, окончания и принудительного прекращения цикла. Цикл начинается с того, что основной задатчик устанавливает активный уровень на линии LFRAME#. С этого момента периферийные устройства только анализируют состояние линий LAD[3:0], прервав любую операцию на шине (если она проводилась). Задатчик может удерживать LFRAME# в активном состоянии более одного периода частоты синхронизации, при этом он даже может произвольно менять состояние LAD[3:0]. Действительным значением поля START будет то, которое имелось на этих линиях перед переходом LFRAME# в пассивное состояние. Если считанное поле START распознается периферийными устройствами, то они должны декодировать весь цикл, а в противном случае — просто дожидаться следующей активации LFRAME# (например, устройства ввода/вывода, не использующие циклы прямого доступа или захвата шины, могут их просто игнорировать). Принудительное прекращение цикла является специальным циклом, так как начинается с установки LFRAME# в активное состояние, а заканчивается установкой поля START со значением 1111. При этом для более уверенного распознавания линия LFRAME# находится в активном состоянии не менее четырех периодов тактовой частоты.

| Поле | Значение | Источник | Число тактов |

|---|---|---|---|

| START | 0 | Основной задатчик | 1 |

| CYCTYPE+DIR | 100 | Основной задатчик | 1 |

| ADDR | ХХХХ | Основной задатчик | 8 |

| TAR | 1111 | Основной задатчик | 2 |

| SYNC | 101 | Периферийное устройство | 3 |

| SYNC | 0 | Периферийное устройство | 1 |

| DATA | ХХХХ | Периферийное устройство | 2 |

| TAR | 1111 | Периферийное устройство | 2 |

| Всего тактов | 20 | ||

| Время доступа | 0,66 мкс | ||

| Скорость передачи | 1,5 Мбайт/с |

В табл. 5 приведены последовательность и характеристики полей в цикле чтения из памяти. Основной задатчик инициирует цикл, определяет тип цикла и направление передачи (чтение из памяти), адрес памяти и информирует об освобождении линий LAD[3:0]. Периферийное устройство во время подготовки данных передает поля SYNC со значением 0101. Когда данные готовы для передачи, устройство передает поле SYNC со значением 0000, две тетрады данных и информирует основного задатчика об освобождении линий LAD[3:0].

Количество полей синхронизации соответствует быстродействию памяти и может изменяться. В данном примере предполагалось наличие ППЗУ с временем доступа 120 нс (4*33 нс = 132 нс). Цикл записи построен примерно так же, но данные передает основной задатчик, а периферийное устройство — только поля SYNC и TAR. В поле SYNC устройство помещает значение либо 0000 (успешная запись), либо 1010 (ошибка при записи). Соответственно возможны варианты, когда устройство не буферизует данные, а выдает поля SYNC до момента реальной записи.

| Поле | Значение | Источник | Число тактов |

|---|---|---|---|

| START | 0 | Основной задатчик | 1 |

| CYCTYPE+DIR | 110 | Основной задатчик | 1 |

| ADDR | ХХХХ | Основной задатчик | 8 |

| DATA | ХХХХ | Основной задатчик | 2 |

| TAR | 1111 | Основной задатчик | 2 |

| SYNC | 0 | Периферийное устройство | 1 |

| TAR | 1111 | Периферийное устройство | 2 |

| Всего тактов | 17 | ||

| Время доступа | 0,56 мкс | ||

| Скорость передачи | 1,8 Мбайт/с |

В табл. 6 приведены последовательность и характеристики полей в цикле чтения из памяти. Совершенно аналогично происходит ввод/вывод при работе с портами, отличие состоит лишь в других значениях полей CYCTYPE+DIR. Для ознакомления с функциями работы с прямым доступом к памяти и управления потребляемой мощностью в табл. 7 приведены необязательные линии интерфейса LPC.

| Наименование | Направление | Назначение | |

|---|---|---|---|

| Периферия | Основной задатчик | ||

| LDRQ# | O | I | Запрос на прямой доступ к памяти или захват шины. Каждому устройству, обладающему этими функциями, требуется отдельная линия LDRQ# |

| SERIRQ | I/O | I/O | Последовательный запрос на прерывание |

| CLKRUN# | OD I/OD | OD I/OD | То же, что и PCI CLKRUN# |

| PME# | OD | I/OD | То же, что и PCI PME# |

| LPCPD# | I O | I O | Отключение, указывает, что периферия должна подготовиться к отключению |

| LSMI# | O/D I | O/D I | Как и PCI SMI#, нужен для повторных попыток |

При запросе прямого доступа к памяти (ПДП) или захвата шины используется линия LDRQ#. В первом случае по ней передается номер канала ПДП, во втором — зарезервированное значение 100. При благоприятном для данного запроса исходе арбитража основной задатчик начинает производить циклы ПДП. Бит LAD[3] в поле CHANNEL играет специальную роль и соответствует линии шины ISA TC (Terminal Count). В случае передачи последней порции данных (1, 2, 4 байт) этот бит устанавливается в 1, сигнализируя о том, что текущий сеанс ПДП закончен. Также сеанс ПДП может быть завершен установкой поля SYNC=0000 (синхронизация достигнута) или SYNC=1010 (ошибка), так как при циклах ПДП для индикации готовности данных используется значение SYNC=1001 (синхронизация достигнута; в следующем цикле будут еще данные). Последовательность полей и другие характеристики цикла ПДП при 8-битном чтении внешним устройством из основной памяти приведены в табл. 8. В зависимости от типа ПДП (8, 16 или 32 разряда) последние четыре поля передаются один, два или четыре раза соответственно. Соответственно будут меняться время доступа и скорость передачи.

Цикл захвата шины, как и все остальные, инициируется основным задатчиком после получения запроса по линии LDRQ#. Основной задатчик, как и при всех других циклах, формирует поле START, имеющее значение 0010 или 0011 (разрешение для задатчика 1 или задатчика 2; в настоящее время поддерживается не более двух задатчиков). После этого основной задатчик передает управление шиной при помощи поля TAR. Далее все протекает как при описанных выше циклах, за одним исключением: поля SYCTYPE+DIR и последующие, которые определяют тип цикла и направление передачи, формируются устройством, получившим право на захват шины.

| Наименование | Направление | Назначение | |

|---|---|---|---|

| Периферия | Основной задатчик | ||

| LDRQ# | O | I | Запрос на прямой доступ к памяти или захват шины. Каждому устройству, обладающему этими функциями, требуется отдельная линия LDRQ# |

| SERIRQ | I/O | I/O | Последовательный запрос на прерывание |

| CLKRUN# | OD I/OD | OD I/OD | То же, что и PCI CLKRUN# |

| PME# | OD | I/OD | То же, что и PCI PME# |

| LPCPD# | I O | I O | Отключение, указывает, что периферия должна подготовиться к отключению |

| LSMI# | O/D I | O/D I | Как и PCI SMI#, нужен для повторных попыток |

Для работы с устройствами, использующими прерывания, используется линия SERIRQ# и одноименный протокол, описанный в спецификации шины PCI «PCI Local Bus Specification, Rev 2.1». Управление включением/выключением периферийных устройств осуществляется при помощи линий LPCPD# и LRST#. При выключении первая из них устанавливается основным задатчиком в низкий уровень, при этом в течение еще не менее 30 мкс на шину подается сигнал тактовой частоты LCLC. Все периферийные устройства при обнаружении низкого уровня на линии LPCPD# обязаны прекратить любую активность на шине и перейти в режим пониженного энергопотребления. Переход к работе происходит при подаче основным задатчиком на линию LPCPD# высокого уровня. Подача тактового сигнала осуществляется заранее, не менее чем за 100 мкс перед установкой высокого уровня LPCPD#. Для правильного перехода внешних устройств в начальное состояние на линии LRST# поддерживается низкий (активный) уровень еще в течение 60 мкс.

Источник