Шины в микропроцессорной системе

В предыдущей главе я рассказывал про цифровую электронику и общее устройство микроконтроллера (МК). А также, что он состоит из процессора, устройств ввода-вывода (УВВ) и устройства памяти. Но я практически ничего не сказал о том, как они общаются между собой. А это весьма важная тема, в которую я и посвящу тебя в этот раз.

Шины и разряды

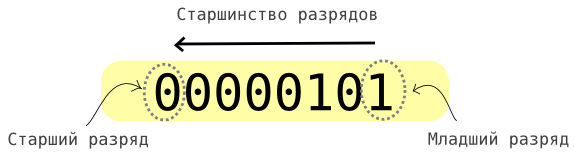

Как ты уже знаешь, вся информация в цифровой технике стараниями инженеров и математиков представляется в виде двоичных чисел, которые записываются с помощью всего двух цифр: «0» и «1». Обычное десятичное число «3» в двоичной записи будет выглядеть как «11», т.е. 310 = 112. Нижние индексы указывают в какой системе счисления записано число, т.е. 10 – десятичная, а 2 – двоичная. Одна цифра в двоичном числе называется разрядом. У разрядов есть старшинство. Самый правый разряд называется младшим, а самый левый – старшим. Старшинство разряда растет справа налево:

Двоичное число, состоящее из 8 разрядов называется 8-ми разрядным, из 16 – шестнадцатиразрядным и т.д. Разрядность двоичного числа имеет самое прямое отношение к взаимодействию между процессором, памятью и устройствами ввода-вывода.

Дело в том, что в твоем МК бегают такие же двоичные числа. Они ходят от памяти к процессору, от процессора назад к памяти или УВВ, а от последних к процессору. Бегают они естественно по проводам (в МК эти шины спрятаны внутри микросхемы). Каждый провод в определённый момент времени может передавать только один разряд со значением «0» или «1». Поэтому, чтобы передать, к примеру, 8-ми разрядное число от процессора к памяти или назад понадобится минимум 8 таких поводов.

Несколько таких проводов, объединенных вместе называются шиной. Шины бывают нескольких видов: шина адреса, шина данных и шина управления. По шине адреса бегают числа, которые обозначают адрес ячейки памяти или устройства ввода-вывода, откуда ты хочешь получить или куда хочешь записать данные. А сами данные будут передаваться уже по шине данных. Это похоже на почтовую посылку. У посылки есть адрес и есть содержание. Так вот в микропроцессорной системе, каковой МК также является, адрес и данные передаются по разным путям, именуемым шинами.

Сколько проводов должно быть в шине?

Это напрямую зависит от конструкции процессора. Процессор может иметь 32-разрядную шину данных и 16-ти разрядное АЛУ. Такие случаи в истории процессоров и МК встречаются многократно. Поэтому разрядность процессора не определяет 100% разрядность шин данных и шин адреса. Всё зависит от конкретной конструкции.

На что влияет разрядность шины адреса

Самым главным, на что она влияет, является количество адресов, которые можно по ней передавать. Например, в 4-разрядной системе это будет всего 2 4 = 16 адресов, в 64-разрядной числов сдресов будет уже 2 64 =18 446 744 073 709 551 616. Таким образом, чем выше разрядность шины адреса, тем к больше объем памяти и больше устройств ввода-вывода, с которыми может работать процессор. Это важно.

На что влияет разрядность шины данных

Её разрядность определяет сколько данных процессор может считать за один раз. Чем выше разрядность, тем больше данных можно считывать за один раз. Её разрядность, как и разрядность шины адреса целиком определяется конструкцией конкретного процессора или МК. Но при этом всегда кратна восьми. Связано это с тем, что практически во всех устройствах памяти минимальной единицей информации является байт, т.е. двоичное число из 8-ми разрядов.

Зачем было нужно вводить ещё одно название: байт? Оно служит для обозначения количества информации. Если количество разрядов говорит просто о длине двоичного числа, то битность говорит о количестве информации, которую это число несет. Считается, что один разряд двоичного числа может передавать 1 бит информации. При этом биты группируются в байты, килобайты, мегабайты, гигабайты, терабайты и т.д.

Кстати, 1 байт = 8 бит, 1 килобайт = 1024 байтам, 1 мегабайт = 1024 килобайтам и т.д. Почему именно 1024? Все это связано с тем, что размер памяти всегда кратен степени двойки: 2 3 = 8, 2 10 =1024. В свою очередь кратность двойке была выбрана благодаря тому, что она упрощает техническую реализацию устройств памяти. Устройство памяти представляет.

Алгоритм работы микроконтроллера

Давай теперь попробуем посмотреть как взаимодействует процессор с памятью и разберёмся зачем нужна шина управления. Любой процессор помимо выполнения арифметических и логических команд умеет делать ещё несколько важных операций: чтение из ячейки памяти, запись в ячейку памяти, чтение из порта ВВ, запись в порт ВВ:

- чтение из ячейки памяти

- запись в ячейку памяти

- чтение из порта ВВ

- запись в порта ВВ

Для того, чтобы указывать какую из этих операций производить используется шина управления. По этой шине от процессора к памяти или портам ввода-вывода передаются сигналы:

| RD (read) | сигнал на чтение |

| WR (write) | сигнал на запись |

| MREQ (memory request) | запрос обращения к памяти |

| IORQ (input/output request) | запрос обращения к портам в/в |

| READY | сигнал готовности |

| RESET | сигнал сброса |

Когда процессору требуется обратиться к памяти он выставляет на шине управления сигнал MREQ, при этом будет выставлен одновременно с ним сигнал RD/WR. Если процессор будет писать в память, то выставляется сигнал WR, если чтение – RD. Тоже самое происходит, если процессор обращается к портам ввода-вывода.

А вот сигнал READY нужен для того, чтобы сообщить процессору, что чтение/запись завершены. Всё довольно просто. Если тебя одолевают вопросы почему несмотря на то, что и память и порты ввода-вывода, через которые подключены внешние устройства, не конфликтуют, то разгадка будет довольно простой. В каждый момент времени процессор обращается только к одному конкретному устройству: либо памяти, либо через порты к портам ввода-вывода. И шина управления обеспечивает правильное разделение доступа.

Все описанное – упрощенная модель микропроцессорной системы, каковой является и персональный компьютер, и микроконтроллер.

Теперь вырисовывается уточнение к алгоритму работу микроконтроллера, который я описывал в прошлой главе. Когда ты подаёшь питание на МК, то он выставляет сигнал на шине управления MREQ, RD, а на шине адреса адрес, по которому в ячейке памяти программ должна находиться первая команда его программы (чаще всего это нулевой адрес памяти программ). Затем МК её выполнит и в зависимости от этой и последующих команд на шине управления, адреса и данных будут появляться соответствующие сигналы и данные.

Подведу итоги:

- Процессор, память и порты ввода-вывода общаются между собой с помощью шин.

- Основные шины бывают нескольких видов: шина данных, шина адреса, шина управления

- Разрядность шины адреса и шины данных определяется конструкцией процессора

Теперь ты продвинулся ещё на шаг в понимании того, как работает цифровая техника и в частности микропроцессорные системы. В следующий раз мы продвинемся еще на шаг к нашей цели — пониманию как устроен мир электроники

Источник

Системная шина микропроцессора

Системная шина процессора предназначена для обмена информацией микропроцессора с любыми внутренними устройствами микропроцессорной системы (контроллера или компьютера). В качестве обязательных устройств, которые входят в состав любой микропроцессорной системы, можно назвать ОЗУ, ПЗУ, таймер и порты ввода-вывода. Структурная схема простейшего микропроцессорного устройства приведена на рисунке 1.

В состав системной шины в зависимости от типа процессора входит одна или несколько шин адреса, одна или несколько шин данных и шина управления. Несколько шин данных и адреса применяется для увеличения производительности процессора и используется только в сигнальных процессорах. В универсальных процессорах и контроллерах обычно применяется одна шина адреса и одна шина данных.

В понятие шины вкладывают разное значение при рассмотрении различных вопросов. В простейшем случае под понятием шина подразумевают параллельно проложенные провода, по которым передаётся двоичная информация. При этом по каждому проводу передаётся отдельный двоичный разряд. Информация может передаваться в одном направлении, как, например, для шины адреса или шины управления, или в различных направлениях (для шины данных). По шине данных информация передаётся либо к процессору, либо от процессора в зависимости от операции записи или чтения, которую в данный момент осуществляет процессор.

В любом случае все сигналы, необходимые для работы системной шины формируются микросхемой процессора как это рассматривалось при изучении операционного блока. Иногда для увеличения скорости обработки информации функции управления системной шины берёт на себя отдельная микросхема (например контроллер прямого доступа к памяти или сопроцессор). Арбитраж доступа к системной шине при этом осуществляет контроллер системной шины (в простейшем случае достаточно сигнала занятости шины).

В некоторых случаях в понятие шина дополнительно включают требования по уровням напряжения, которыми представляются нули и единицы, передаваемые по её проводам. В состав требований могут быть включены длительности фронтов передаваемых сигналов, типы используемых разъёмов и их распайка, последовательность передаваемых сигналов и скорость их передачи.

Рисунок 1. Структурная схема подключения микропроцессорных устройств к системной шине

При подключении различных устройств к системной шине возникает вопрос — как различать эти устройства между собой? Единственный способ сделать это использовать индивидуальный адрес для каждого устройства, подключенного к системной шине микропроцессора. Так как адресация производится к каждой ячейке устройства индивидуально, то возникает понятие адресного пространства, занимаемого каждым устройством и адресного пространства микропроцессорного устройства в целом.

Адресное пространство микропроцессорного устройства.

Адресное пространство микропроцессорного устройства изображается графически прямоугольником, одна из сторон которого представляет разрядность адресуемой ячейки этого микропроцессора, а другая сторона — весь диапазон доступных адресов для этого же микропроцессора. Обычно в качестве минимально адресуемой ячейки памяти выбирается восьмиразрядная ячейка памяти (байт). Диапазон доступных адресов микропроцессора определяется разрядностью шины адреса системной шины. При этом минимальный номер ячейки памяти (адрес) будет равен 0, а максимальный определяется из формулы:

Для шестнадцатиразрядной шины это будет число 65535 (64K). Адресное пространство этой шины и распределение памяти микропроцессорной системы, изображённой на рисунке 1, приведено на рисунке 2, а распределение памяти микропроцессорной системы, изображённой на рисунке 1, приведено на рисунке 3.

Рисунок 2. Адресное пространство шестнадцатиразрядной шины адреса

Рисунок 3. Распределение памяти микропроцессора с шестнадцатиразрядной шиной адреса

Микропроцессоры после включения питания и выполнения процедуры сброса всегда начинают выполнение программы с определённого адреса, чаще всего нулевого. Однако есть и исключения. Например процессоры, на основе которых строятся универсальные компьютеры IBM PC или Macintosh стартуют не с нулевого адреса. Программа должна храниться в памяти, которая не стирается при выключении питания, то есть в ПЗУ.

Выберем для построения микропроцессорной системы микросхему ПЗУ объёмом 2 килобайта, как это показано на рисунке 1. При рассмотрении построения блока обработки сигналов мы договорились, что процессор после сброса начинает работу с нулевого адреса, поэтому разместим ПЗУ в адресном пространстве начиная с нулевого адреса. Для того, чтобы нулевая ячейка ПЗУ оказались расположенной по нулевому адресу адресного пространства микропроцессора, старшие разряды шины адреса должны быть равны 0.

При построении схемы необходимо декодировать старшие пять разрядов адреса (определить, чтобы они были равны 0). Это выполняется при помощи дешифратора адреса, который в данном случае вырождается в пятивходовую схему «ИЛИ» Это связано с тем, что внутри ПЗУ уже есть одиннадцативходовый дешифратор адреса. При использовании дешифратора адреса, обращение к ячейкам памяти выше двух килобайт не приведёт к чтению ячеек ПЗУ, так как на входе выбора кристалла CS уровень напряжения останется высоким.

Теперь подключим микросхему ОЗУ. Для примера выберем микросхему объёмом 8 Кбайт. Для выбора любой из ячеек этой микросхемы достаточно тринадцатибитового адреса, поэтому необходимо дополнительно декодировать три оставшихся разряда адреса. Так как начальные ячейки памяти адресного пространства уже заняты ПЗУ, то использовать нельзя. Выберем следующую комбинацию цифр 001 и используем известные нам принципы построения схемы по произвольной таблице истинности. Дешифратор адреса выродится в данном случае в трёхвходовую схему «И-НЕ» с двумя инверторами на входе. Схема этого дешифратора приведена на рисунке 1. Приведённый дешифратор адреса обеспечивает нулевой уровень сигнала на входе CS только при комбинации старших бит 001. Обратите внимание, что так как объём ПЗУ меньше объёма ОЗУ, то между областью адресов ПЗУ и областью адресов ОЗУ образовалось пустое пространство неиспользуемых адресов памяти.

И, наконец, так как все микропроцессоры предназначены для обработки данных, поступающих извне, то в любой микропроцессорной системе должны присутствовать порты ввода-вывода. Порт ввода-вывода отображается в адресное пространство микропроцессорного устройства как одиночная ячейка памяти, поэтому порт ввода вывода можно разместить по любому свободному адресу. Проще всего построить дешифратор числа FFFFh. В этом случае дешифратор превращается в обычную 16-ти входовую схему «И-НЕ», поэтому и выберем эту ячейку памяти в адресном пространстве микропроцессора для размещения порта ввода-вывода.

Способы расширения адресного пространства микропроцессора.

Известно, что размер адресного пространства определяется разрядностью счётчика команд микропроцессора. Достаточно часто при развитии микропроцессорной системы возможности адресного пространства исчерпываются. В таком случае приходится прибегать к методам расширения адресного пространства.

Для расширения адресного пространства можно воспользоваться параллельным портом. Внешние выводы параллельного порта при этом используются в качестве старших битов адресной шины. Такой метод расширения адресного пространства называется страничным методом адресации. Регистр данных параллельного порта при использовании его для расширения адресного пространства будет называться переключателем страниц. Схема использования параллельного порта в качестве переключателя страниц памяти приведена на рисунке 4.

Рисунок 4. Использование параллельного порта в качестве переключателя страниц памяти

В этой схеме параллельный порт используется в качестве простейшего контроллера памяти микропроцессорного устройства. При применении восьмиразрядного параллельного порта в микропроцессорной системе появились дополнительные восемь линий адреса. В результате адресное пространство микропроцессорной системы увеличилось до 16 Мегабайт. Структура нового адресного пространства приведена на рисунке 5, а принцип формирования нового адреса с использованием переключателя страниц приведён на рисунке 6.

Рисунок 5. Структура страничного адресного пространства

Рисунок 6. Формирование адреса с использованием переключателя страниц

Метод страничной адресации прост в реализации и при формировании адреса физической памяти не приводит к дополнительным временным задержкам, но при использовании многозадачного режима работы процессора для каждой активной задачи выделяется целая страница в системной памяти микропроцессора. При такой работе в системной памяти процессора остаётся много неиспользуемых областей. Решить возникшую проблему позволяет метод сегментной организации памяти.

При сегментном методе организации памяти для расширения адресного пространства используется базовый регистр, относительно которого производится адресация команд или данных в программе. Разрядность базового регистра обычно выбирают равной разрядности счётчика команд. В качестве базового регистра, как и при страничной организации памяти, можно использовать параллельный порт.

Для формирования физического адреса используется параллельный двоичный сумматор. На входы этого сумматора подаётся содержимое базового регистра и содержимое счётчика команд. Суммирование производится со смещением содержимого базового регистра влево на несколько бит относительно счётчика команд (рисунок 8). В результате максимальный размер сегмента определяется разрядностью программного счётчика, а максимальная неиспользуемая область памяти — смещением базового регистра относительно программного счётчика.

Адресное пространство при использовании сегментного метода адресации приведено на рисунке 7.

Рисунок 7. Пример адресного пространства с разделением на сегменты

Количество сегментов определяется количеством базовых регистров. Сегменты могут перекрываться в адресном пространстве, и тем самым может регулироваться размер памяти, который отводится под каждый конкретный сегмент памяти. В компьютерах семейства IBM PC имеются четыре базовых регистра, определяющих сегмент данных, сегмент программы, сегмент стека и дополнительный сегмент. Информацию в базовые регистры заносит операционная система при переключении задач.

Рисунок 8. Формирование адреса при сегментной адресации

Ещё одним распространённым способом увеличения адресного пространства является применение окон. При использовании окон производится расширение не всего адресного пространства, а только его части. Внутри адресного пространства выделяется некоторая область, которая называется окном. В это окно может отображаться часть другого адресного пространства.

При использовании окон может быть использован как страничный метод отображения адресного пространства, так и сегментный метод отображения адресного пространства в окно.

При использовании страничного метода отображения, конкретная страница другого адресного пространства, которая в данный момент отображается в окно памяти, определяется переключателем страниц, построенному по такому же принципу как это было рассмотрено на рисунке 4.

При использовании сегментного метода отображения, конкретная область адресного пространства, которая будет отображаться в окно, определяется содержимым базового регистра. Если разрядность адреса вспомогательного адресного пространства, отображаемого в окно основной памяти, совпадает с разрядностью базового регистра, то любая область вспомогательной памяти может быть отображена в основную память с точностью до байта.

Принцип построения оконной адресации при отображении страниц показан на рисунке 9.

Рисунок 9. Применение окна для расширения адресного пространства

Оконная адресация часто используется при развитии микропроцессорных семейств, когда размера областей памяти, отведённых для конкретных задач в младших моделях семейства, не хватает для старших моделей семейства, а при этом нужно поддерживать аппаратную совместимость с младшими моделями семейства. В качестве примера можно привести микросхемы I81c96 фирмы INTEL или TMS320c5410 фирмы Texas Instrument, где для расширения области регистров специальных функций используется оконная адресация.

Понравился материал? Поделись с друзьями!

Вместе со статьей «Системная шина микропроцессора» читают:

Источник